热点资讯

咨询热线:

027-87538900

邮件: wangting@whhexin.com

电话:18062095810

地址: 湖北·武汉·鲁巷·华乐商务中心1006

TERASIC友晶板卡DE1-SOC|Intel FPGA开发平台加密烧录方法

在竞争日益激烈的商业以及军事环境中,设计安全对于数字设计人员而言是一个至关重要的考虑因素。随着 FPGA 在更庞大、更关键的系统组件中扮演着愈来愈重要的角色,保护设计免受非法复制、逆向工程以及篡改也愈加显得重要。

FPGA 内嵌一个专用的解密模块,通过运用 AES算法 ( 一种行业标准的加密算法 ) 对用户自定义的 256-bit 密钥的配置数据进行解密,必须在接收到加密数据前,将自定义的 256- bit 密钥写入器件中。如果没有使用安全特性,那么 AES 解密器将被旁路。当使用设计安全特性时,密钥被存储在 FPGA 中,能够防止未经授权的复制、逆向工程以及篡改。

FPGA既支持易失性密钥存储,也支持非易失性密钥存储。其中,易失性密钥需要电池来存储和更新密钥,而非易失性密钥存储不需要电池,只需对一个密钥进行编程,不需要电池。在本文中,我们将以DE1-SoC开发板为例,具体描述如何在FPGA上对设计代码进行非易失性密钥加密(支持烧写非易失性密钥的Blaster下载器工具有 Intel Ethernet Blaster Cable 和 Intel UB2 Blaster Cable,这里以Intel FPGA Ethernet Cable来进行操作)。

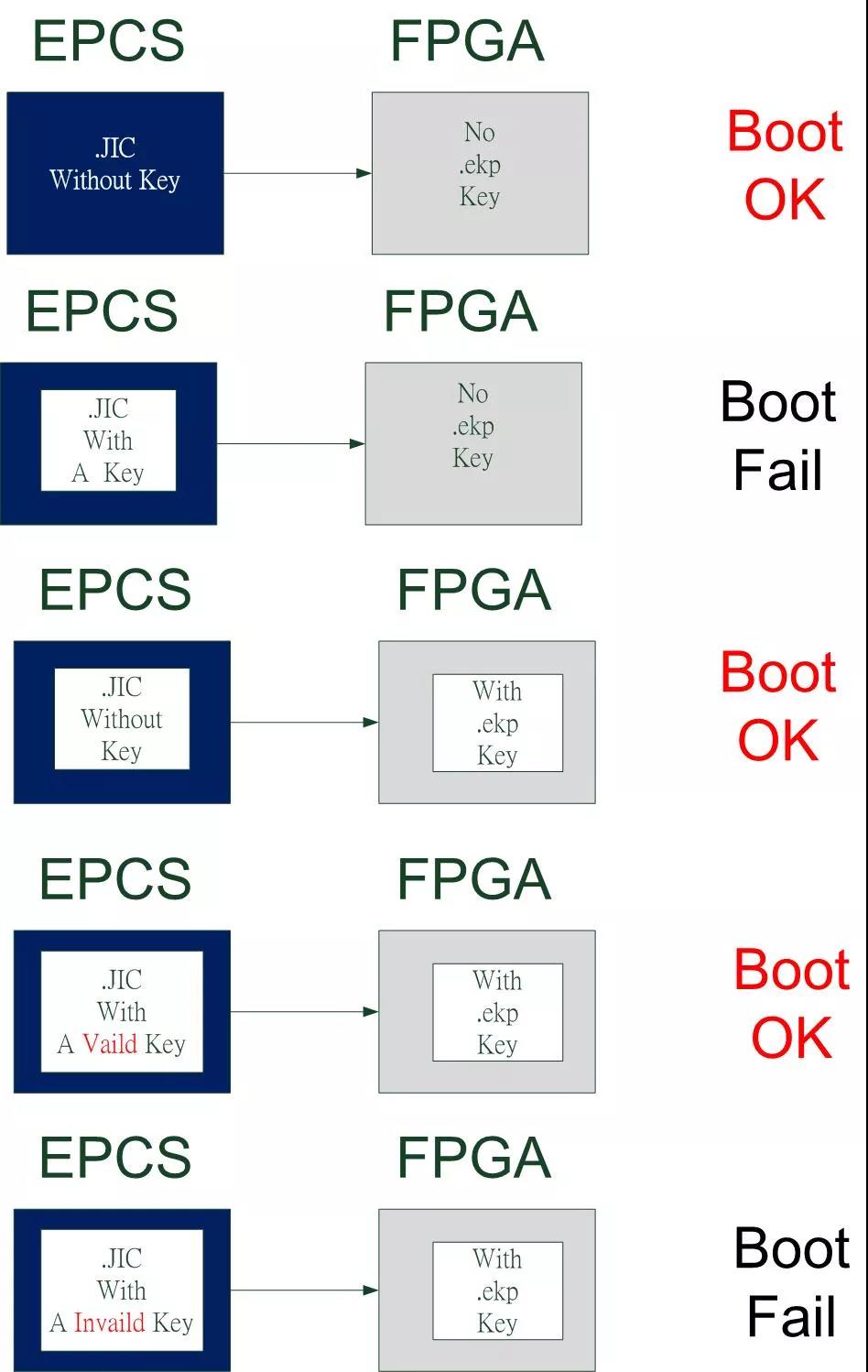

首先,我们来了解下非易失性密钥(non-volatile security key)加密原则,如下图:

那使用DE1-SoC开发板来对设计代码进行非易失性密钥加密,具体该怎么操作呢?

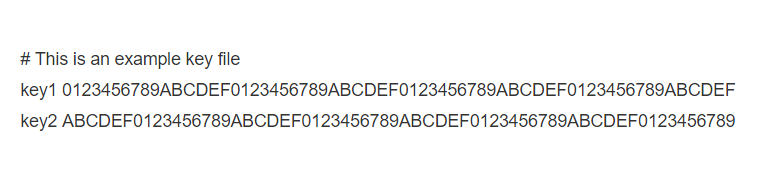

Step 1:准备好加密Key,存档为 x.key。

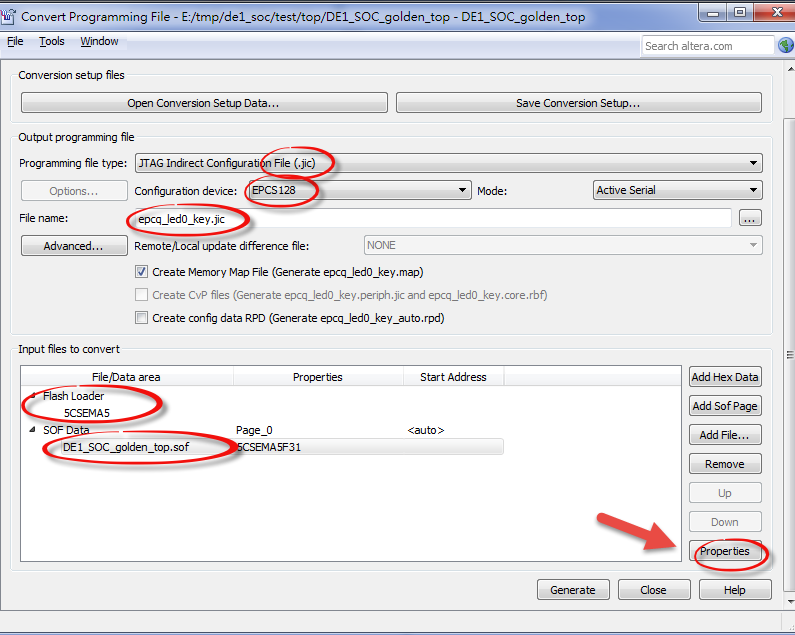

Step 2:在Quartus软件中,使用Convert Programming File 产生 .ekp文件,烧录FPGA (即在FPGA内设定non-volatle key)。

首先,在生成jic文件前,点击sof 文件,选择Properties:

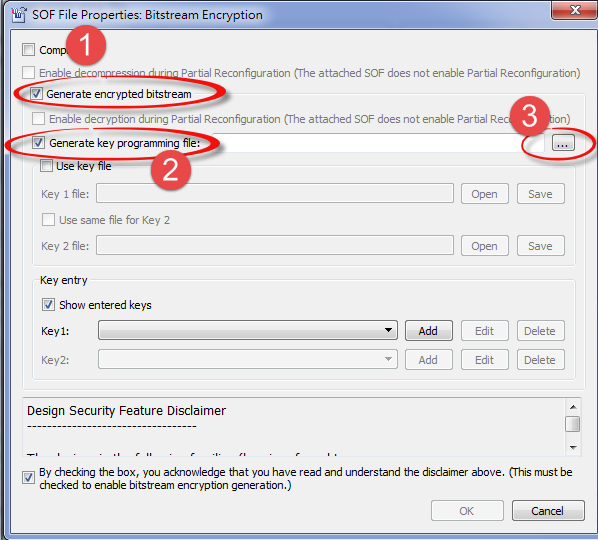

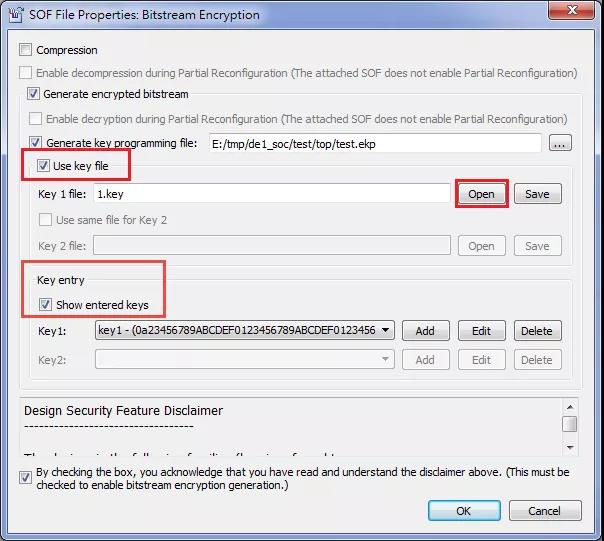

其次,设定生成sof的文件信息:

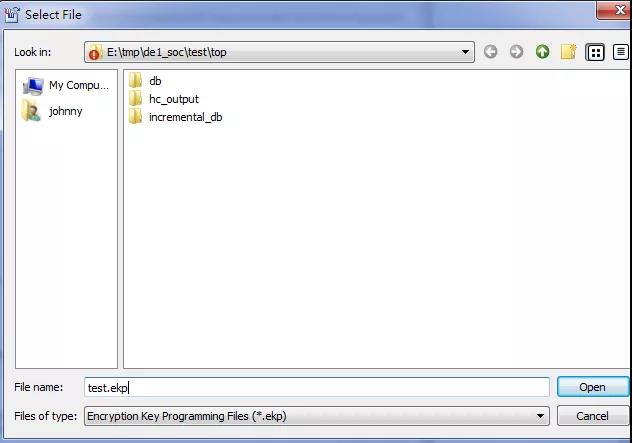

最后,命名和存档.ekp文件:

Step 3:产生加密的 jic 文件。

首先,打开加密Key 文件,勾选Key entry:

在完成添加后,返回上级菜单。点击Generate按钮,生成.jic文件。

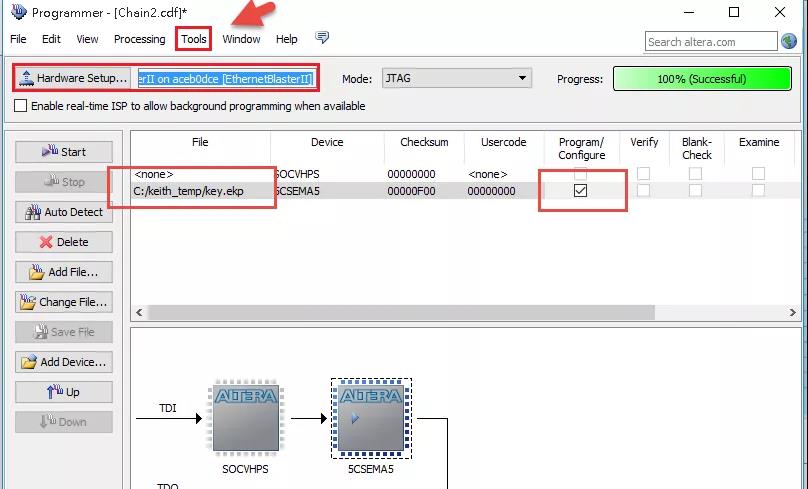

Step 4:打开Quartus Programer 程序,烧录非易失性密钥。

烧录非易失性密钥时,需要用到Intel Ethernet Blaster Cable, 因此,先在Hardware处选择Ethernet Blaster ,再在Tools 菜单栏下选择Option: Tools --> Options,取消Configure volatile design security key when avaliable前的勾选符号。然后,选择刚产生的.ekp文件下载到FPGA中。(注意:下载成功后,就不可再烧写其他加密程序了!!!)

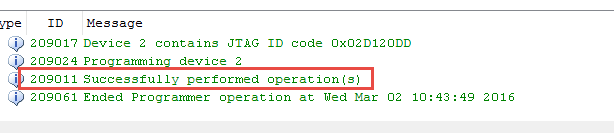

如果出现以下信息,代表成功烧录了.ekp 文件:

Step 5:测试。

烧录加密的.jic 文件,如果开发板可以成功运行该加密程序,则说明加密操作成功。

欲知更多产品和应用详情,您还可以通过如下方式联系我们:

邮箱:wangting@whhexin.com

电话:027-87538900/18062095810(王小姐)